3D封装与系统级封装的背景体系解析介绍

3D封装与系统级封装概述

一、引言:先进封装技术的演进背景

随着摩尔定律逐渐逼近物理极限,半导体行业开始从单纯依赖制程微缩转向封装技术创新。3D封装和系统级封装(SiP)作为突破传统2D平面集成限制的核心技术,正在重塑电子系统的集成范式。3D封装通过垂直堆叠实现超高的空间利用率,而SiP则专注于多功能异质集成,两者共同推动着高性能计算、人工智能和物联网等领域的技术革新。

根据Mordor Intelligence报告,全球2.5D/3D封装市场规模已从2023年的86.6亿美元增长至2029年的216.3亿美元,年复合增长率达17.2%。这种爆发式增长源于三大技术驱动力:HBM存储器需求激增、AI芯片对带宽的渴求,以及移动设备对微型化的极致追求。

二、3D封装技术体系解析

2.1 技术原理与核心要素

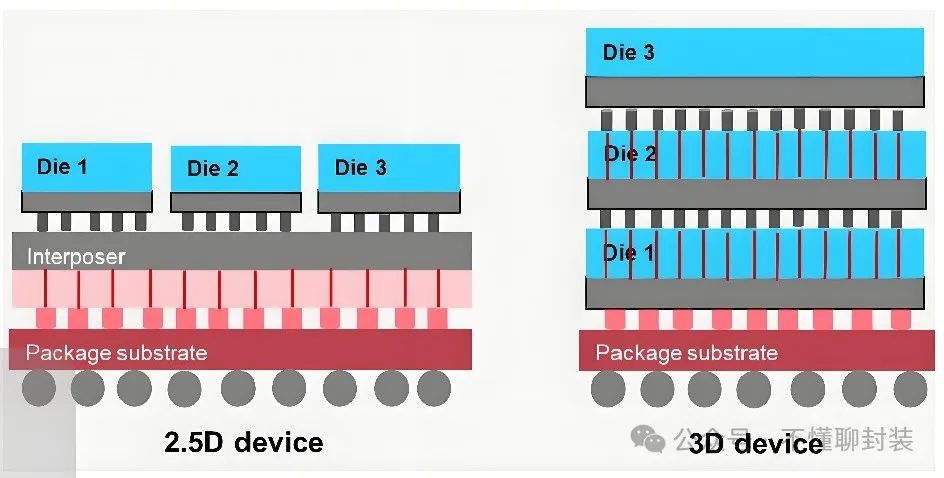

3D封装的核心在于垂直互连架构的实现,其技术突破点体现在三个维度:

硅通孔(TSV)技术:在芯片内部制作直径5-50μm的垂直导电通道,实现层间直接电气连接。英特尔的Foveros技术采用10μm级TSV,使互连密度达到传统键合的100倍。

混合键合(Hybrid Bonding):通过铜-铜直接键合实现1μm以下间距互连,台积电的SoIC技术已将此工艺良率提升至99.4%,显著降低RC延迟。

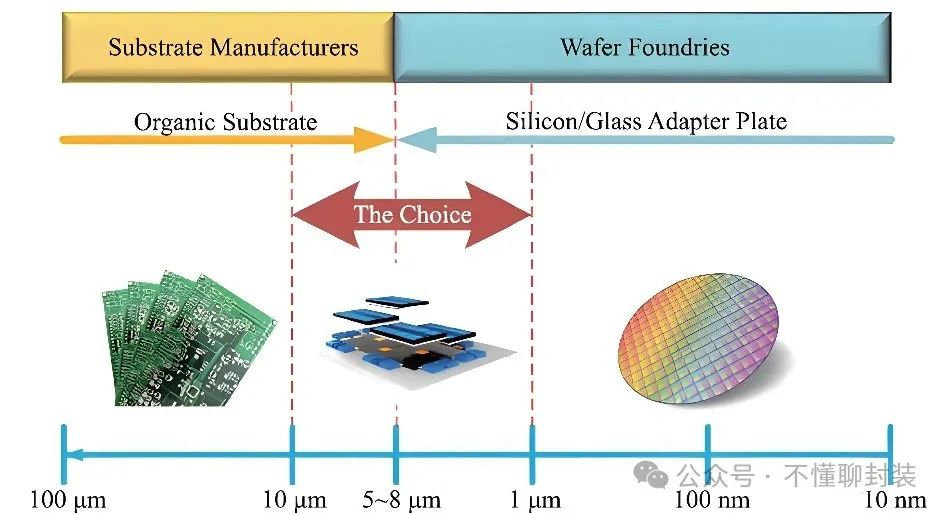

转接板:从硅基转接板(如CoWoS的1700mm²超大尺寸)到玻璃基板(TGV),材料选择直接影响信号完整性和热膨胀匹配。

2.2 典型实现方案对比

2.3关键技术挑战

热管理:堆叠结构导致热流密度激增,AMD的3D V-Cache采用非对称布局将热点温度控制在85℃以下。

机械应力:TSV引起的局部应力可达200MPa,需通过应力缓冲层和环形栅结构补偿。

测试策略:采用IEEE 1838标准构建边界扫描链,实现95%以上的堆叠前芯片筛选率。

三、系统级封装(SiP)的技术演进

3.1 技术定义与架构创新

SiP通过三维异质集成将处理器、存储器、传感器等不同制程/材料的元件整合于单一封装。高通的Snapdragon 8 Gen1将8核CPU、GPU、5G基带等10+芯片集成,封装体积缩减30%的同时功耗降低22%。

关键技术突破点:

1.埋置式结构:将无源器件嵌入有机基板,村田的0402尺寸电感集成度提升5倍。

2.扇出型封装:台积电InFO技术实现4μm RDL线宽,支持5000+ I/O的处理器封装。

3.柔性互连:应用液态金属互连技术,弯曲半径可达3mm仍保持10^8次循环可靠性

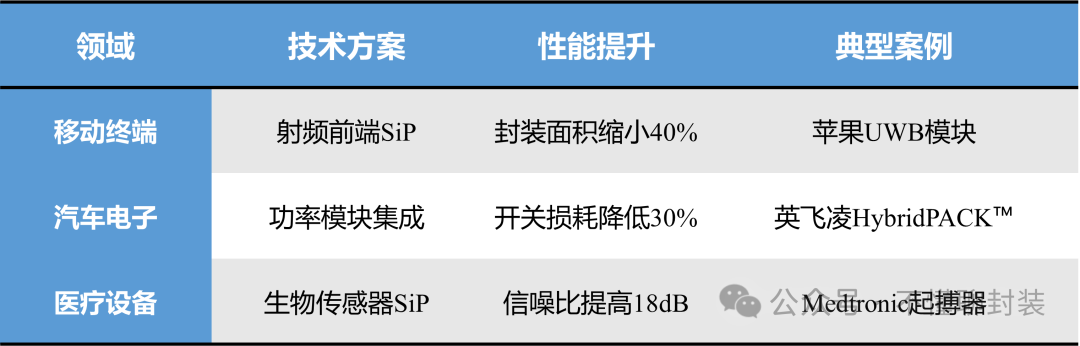

3.2 典型应用场景分析

结语

从3D封装带来的垂直革命到SiP实现的系统级创新,先进封装技术正在书写半导体行业的第二增长曲线。随着混合键合、光子集成等技术的成熟,封装已从单纯的保护功能进化为决定系统性能的核心要素。未来十年,3D/SiP技术将与AI、量子计算等前沿领域深度耦合,推动电子系统向更高维度演进,最终实现"封装即芯片"的产业新范式。